The MT41K128M16JT-125

is a DRAM chip produced by Micron Technology, part of its DDR3 SDRAM product line. Here are its main features and description:

Description:

- Capacity: 2 Gb (2 gigabits)

- Organization: 128M x 16 (128M x 16 bits)

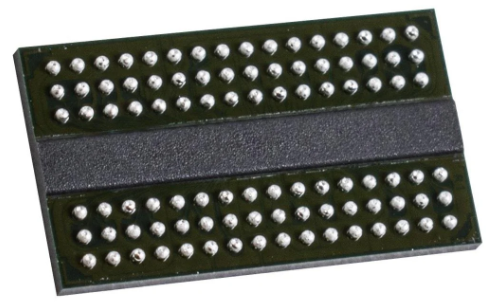

- Package Type: FBGA (Fine-Pitch Ball Grid Array), with the specific package code “JT”

- Speed Grade: DDR3-1600 (1600 MT/s), denoted as -125, indicating a clock cycle time of 1.25 ns

- Operating Voltage: 1.5V

- Temperature Range: Industrial temperature range (with possible extended temperature range options)

Key Features:

- Data Rate: Up to 1600 MT/s (Megatransfers per second)

- CAS Latency (CL): 11 clock cycles (CL = 11)

- Row Cycle Delay (tRCD): 11 clock cycles

- Row Precharge Time (tRP): 11 clock cycles

- Refresh Cycle: Standard and low power modes, with a 7.8 µs refresh cycle

- Memory Configuration: 8 bank groups, each with 8 banks (total of 64 banks)

- Prefetch Buffer: Supports 8-bit prefetch

- Self-Refresh and Auto Temperature-Compensated Self-Refresh: Provides better power management in low power states

- Deep Power-Down Mode: Supports deep power-down mode for reduced power consumption

Applications:

This DRAM chip is typically used in high-performance computing, servers, consumer electronics, networking equipment, and other applications that require high bandwidth and low latency memory.

Package Dimensions:

- The package size is usually a 78-ball FBGA (9mm x 11.5mm). For specific dimensions and pin layout, refer to the product datasheet.

Reference Documents:

For detailed technical specifications, pin descriptions, electrical characteristics, timing diagrams, and application guidelines, it is recommended to refer to the product datasheet and application notes provided by Micron Technology. These documents are typically available on Micron Technology’s official website.

Lead free / RoHS Compliant

Lead free / RoHS Compliant